#### Ampère Unité Mixte de Recherche CNRS

Génie Électrique, Électromagnétisme, Automatique, Microbiologie environnementale et Applications

# State of the art of high switching frequency inductive DC-DC converters in SoC context

B. Allard, Florian Neveu, C. Martin

Ampere, Lyon

www.ampere-lab.fr

#### **Abstract**

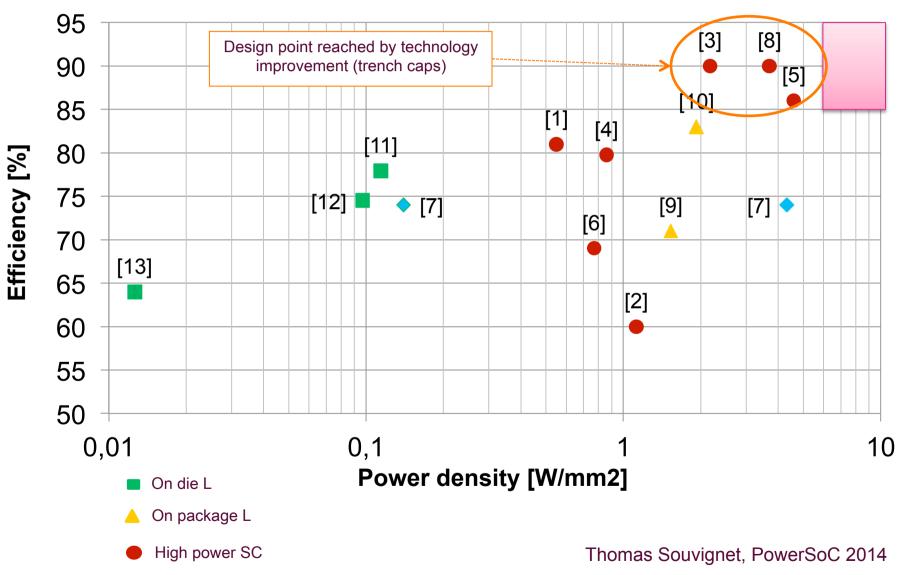

- Supplying large system on chip requires specific grid and is spread over multiple voltage domains. Each domain depends on a dedicated DC-DC. For the sake of integration, switch capacitor DC-DC seems to have the favors of designers but further increase in the switching frequency associated to a 3D approach gives back some competitiveness to inductive DC-DC converters.

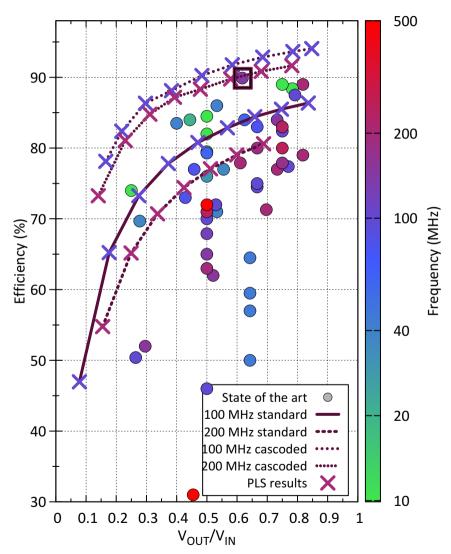

- Some recent experiments in the +100 MHz switching frequency area demonstrate the interest of multiphase and coupled inductors. A global analysis of pertinent results as state of the art enables to draw similar conclusions and many other trends.

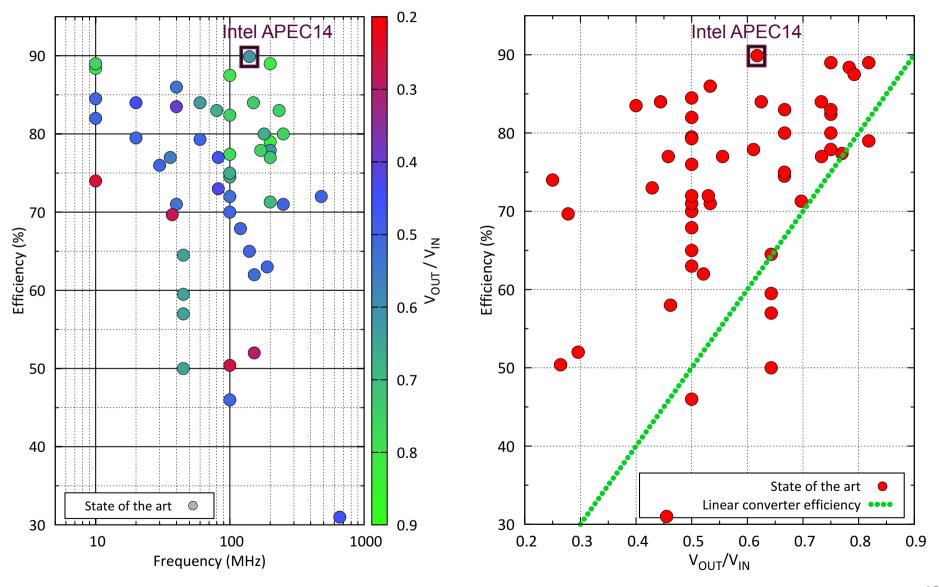

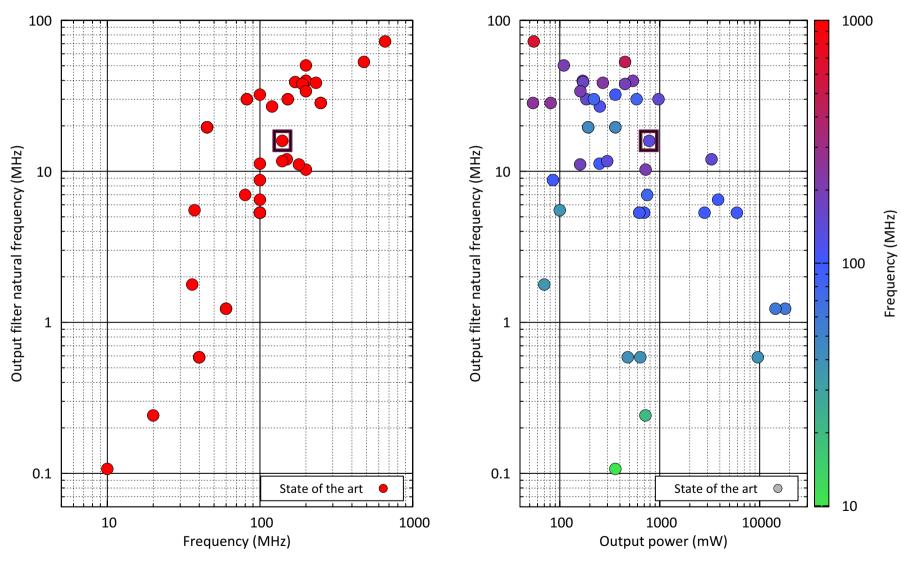

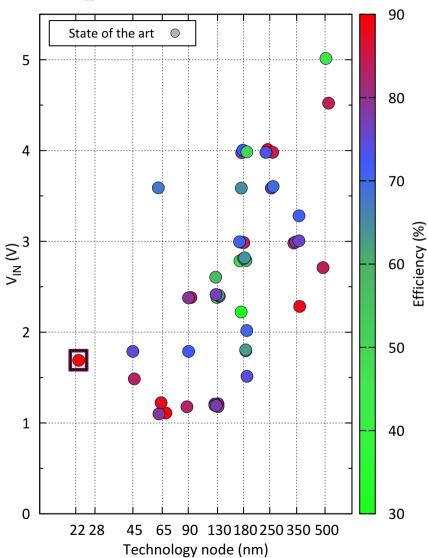

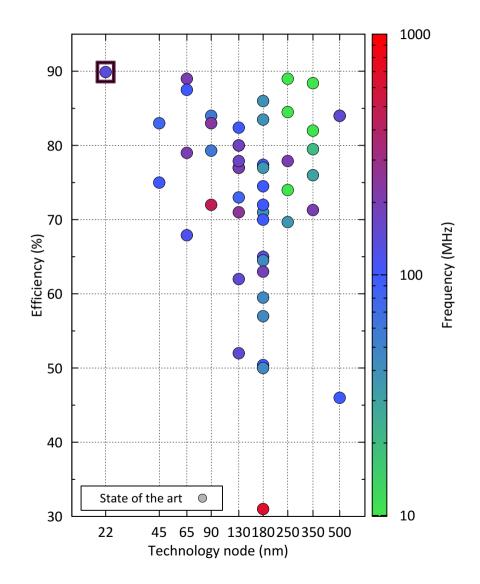

- Various landscapes have been populated with available figures in pertinent papers about implemented DC-DC converters. Trends are analyzed to exhibit design trade-offs and further extrapolations, focusing mainly on active devices.

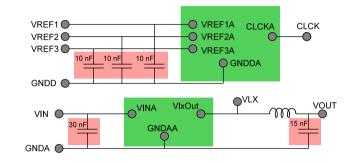

- In the context of POWERSWIPE project, a 200 MHz DC-DC converter (3.3 V input voltage, 350 mW output power, 1.2 V to 0.6 V output voltage) is taken as a study case. Specifications are added in the landscape and the trend analysis orientates the converter architecture for 40 nm CMOS technology. Particularly, cascode-based power stage is analyzed and selected. Primary post-layout simulation results let hope more than 90% power efficiency. Passive devices are related to an interposer technology targeting the fabrication of magnetic devices on top of embedded capacitor banks.

- **Remember PowerSoC 2012**

- **♦ Inductive vs. capacitive (non-isolated) DC/DC**

- **♦ Why +100MHz switching frequency DC/DC?**

- **A** possible lecture of the state-of-the-art

- SpowerSWIPE proposal, early results

- **Perspectives**

### PowerSoC 2012

- Now established: "power is not an afterthought of system"

- Specifications now common in essence

- how to deliver as much Amps as possible in a given area, for a targeted quality of service, with the best efficiency and the lowest cost

- Higher expectations: losses < 10% of platform power + efficiency flatness

- SGlobal view: passives as important as actives

- Complex control schemes despite high switching frequency

#### Non-isolated DC/DC converters

# Inductive versus capacitive architectures

- SoA → efforts to push the limits

- SoC → heavy technology constraint

- V<sub>out</sub>/V<sub>in</sub> specification

- Necessity for a portfolio of solutions with various tradeoffs

# Capacitive on-chip DC/DC

State of the art of high switching frequency inductive DC-DC converters

#### Non-isolated DC/DC converters

# Why +100MHz switching frequency?

- Improvements in technology enables better active and passive devices

mechanical increase in frequency thus in footprint

- Application requirements

- large transient performances (EER, DVFS)

- power density (smaller footprint)

- Mission profile (efficiency flatness)

# Why +100MHz switching frequency?

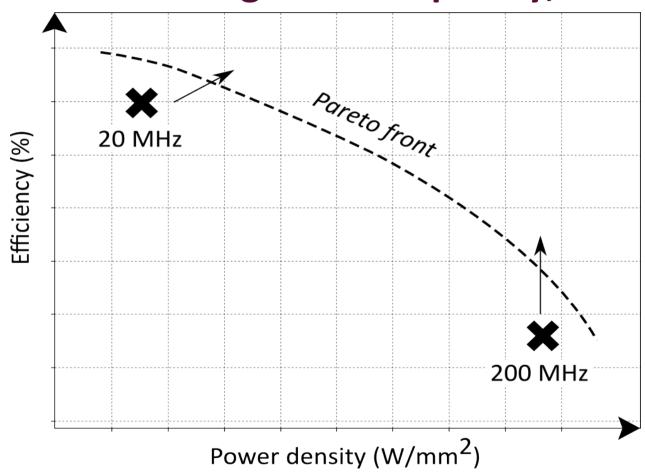

# **♦** Losses → limit voltage and frequency, but...

J.W. Kolar et al., "PWM Converter Power Density Barriers", IEEE PCC, 2007

## State-of-the-art of HF DC-DC

### Silicon demonstrators

- Steady-state performances

- Transient performances, Power density aspects: no common benchmarks

# Many metrics, unique FoM not pertinent → landscapes

# Reference point :

[Burton et al., 2014] Fully integrated voltage regulators on 4th generation Intel core SoCs. In 29th Annual IEEE Applied Power Electronics Conference and Exposition (APEC), 2014, pages 432-439.

CIPS 2014: Neveu, F.; Martin, C.; Allard, B., "Review of high frequency, highly integrated inductive DC-DC converters", 8th International Conference on Integrated Power Systems (CIPS), 2014, pp.1-7, 25-27 Feb. 2014

#### State of the art - References

[Abedinpour et al., 2007] A multistage interleaved synchronous buck converter with integrated output filter in 0.18 um sige process. Power Electronics, IEEE Transactions on, 22(6):2164-2175.

[Alimadadi et al., 2009] A fully integrated 660 mhz low-swing energy-recycling dc-dc converter. Power Electronics, IEEE Transactions on, 24(6):1475-1485.

[Bathily et al., 2012] A 200 MHz integrated buck converter with resonant gate drivers for an RF power amplifier. Power Electronics, IEEE Transactions on, 27(2):610-613.

[Bergveld et al., 2009] 65-nm-cmos 100-mhz 87dual-die system-in-package integration. In Energy Conversion Congress and Exposition, 2009. ECCE 2009. IEEE, pages 3698-3705.

[Blanken et al., 2008] A 50mhz bandwidth multi-mode pa supply modulator for gsm, edge and umts application. In Radio Frequency Integrated Circuits Symposium, 2008. IEEE, pages 401-404.

[Burton et al., 2014] Fully integrated voltage regulators on 4th generation intel core socs. In Applied Power Electronics Conference and Exposition (APEC), 2014 29th Annual IEEE, pages 432-439.

[Gong et al., 2011] An 80% peak efficiency, 0.84mW sleep power consumption, fully-integrated dc-dc converter with buck/Ido mode control. In Custom Integrated Circuits Conference (CICC), 2011 IEEE, pages 1-4.

[Hannon et al., 2009] A 20 mhz 200-500 ma monolithic buck converter for rf applications. In Applied Power Electronics Conference and Exposition, 2009. APEC 2009. Twenty-Fourth Annual IEEE, pages 503–508. [Hazucha et al., 2005] A 233-MHz 80%-87% efficient four-phase DC-DC converter utilizing air-core inductors on package. Solid-State Circuits, IEEE Journal of, 40(4):838–845.

[Huang and Mok, 2013An 82.4% efficiency package-bondwire-based four-phase fully integrated buck converter with flying capacitor for area reduction. In Solid-State Circuits Conference Digest of Technical Papers

(ISSCC), 2013 IEEE International, pages 362–363.

[Ishida et al., 2010] 3d stacked buck converter with 15 um thick spiral inductor on silicon interposer for fine-grain power-supply voltage control in sip's. In 3D Systems Integration Conference (3DIC), 2010 IEEE International, pages 1–4.

[Kim et al., 2012] A fully-integrated 3-level dc-dc converter for nanosecond-scale dvfs. Solid-State Circuits, IEEE Journal of, 47(1):206-219.

[Kudva and Harjani, 2011] Fully-integrated on-chip dc-dc converter with a 450x output range. Solid-State Circuits, IEEE Journal of, 46(8):1940–1951.

[Li et al., 2011] A 90-240 mhz hysteretic controlled dc-dc buck converter with digital phase locked loop synchronization. Solid-State Circuits, IEEE Journal of, 46(9):2108–2119.

[Li, 2012] A fully-integrated buck converter design and implementation for on-chip power supplies. Journal of Computers, 7(5):1270–1277.

[Lu et al., 2012] A 1500ma, 10mhz on-time controlled buck converter with ripple compensation and efficiency optimization. In Applied Power Electronics Conference and Exposition (APEC), 2012 Twenty-Seventh Annual IEEE, pages 1232 –1237.

[Maity et al., 2011] Design of a 20 mhz dc-dc buck converter with 84 percent efficiency for portable applications. In VLSI Design, 2011 24th International Conference on, pages 316–321.

[Onizuka et al., 2006] Stacked-chip implementation of on-chip buck converter for power- aware distributed power supply systems. In Solid-State Circuits Conference, 2006. ASSCC 2006. IEEE Asian, pages 127 –130. [Ostman et al., 2014] A 3.6-to-1.8-v cascode buck converter with a stacked lc filter in 65-nm cmos. Circuits and Systems II: Express Briefs, IEEE Transactions on, PP(99):1–5.

[Peng et al., 2013] A 100 mhz two-phase four-segment dc-dc converter with light load efficiency enhancement in 0.18 µm cmos. Circuits and Systems I: Regular Papers, IEEE Transactions on, 60(8):2213–2224.

[Peng et al., 2011] High efficiency, high switching speed, algaas/gaas p-hemt dc-dc converter for integrated power amplifier modules. Analog Integrated Circuits and Signal Processing, 66:331-348.

[Schrom et al., 2004] A 480-mhz, multi-phase interleaved buck dc-dc converter with hysteretic control. In Power Electronics Specialists Conference, 2004. PESC 04. 2004 IEEE 35th Annual, volume 6, pages 4702–4707 Vol.6.

[Schrom et al., 2007] A 100mhz eight-phase buck converter delivering 12a in 25mm2 using air-core inductors. In Applied Power Electronics Conference, APEC 2007 - Twenty Second Annual IEEE, pages 727 - 730.

[Song et al., 2014a] A vhf-level fully integrated multi-phase switching converter using bond-wire inductors and on-chip decoupling capacitors and dll phase synchronization. In Applied Power Electronics Conference and Exposition (APEC), 2014 Twenty-Ninth Annual IEEE.

[Song et al., 2014b] A 6a 40mhz four-phase zds hysteretic dc-dc converter with 118mv droop and 230ns response time for a 5a/5ns load transient. In Solid-State Circuits Conference Digest of Technical Papers (ISSCC), 2014 IEEE International, pages 80–81.

[Sturcken et al., 2013] A 2.5d integrated voltage regulator using coupled-magnetic-core inductors on silicon interposer. Solid-State Circuits, IEEE Journal of, 48(1):244–254.

[Sturcken et al., 2011] An integrated four-phase buck converter delivering 1a/mm2 with 700ps controller delay and network-on-chip load in 45-nm soi. In Custom Integrated Circuits Conference (CICC), 2011 IEEE, pages 1–4.

[Sun et al., 2007] 3d power delivery for microprocessors and high-performance asics. In Applied Power Electronics Conference, APEC 2007 - Twenty Second Annual IEEE, pages 127–133.

[Villar and Alarcon, 2008] Monolithic integration of a 3-level dcm-operated low-floating-capacitor buck converter for dc-dc step-down conversion in standard cmos. In Power Electronics Specialists Conference, 2008. PESC 2008. IEEE, pages 4229 –4235.

[Wens and Steyaert, 2008] A fully-integrated 0.18 um cmos dc-dc step-down converter, using a bondwire spiral inductor. In Custom Integrated Circuits Conference, 2008. IEEE, pages 17–20.

[Wens and Steyaert, 2011] A fully inte-grated cmos 800-mw four-phase semi constant on/off-time step-down converter. Power Electronics, IEEE Transactions on, 26(2):326–333.

[Wibben and Harjani, 2008] A high- efficiency dc-dc converter using 2 nh integrated inductors. Solid-State Circuits, IEEE Journal of, 43(4):844-854.

# Efficiency, frequency and ratio

# **Output filter**

# **Technology**

#### **Control schemes**

- Voltage mode versus current mode

- >PWM versus Hysteretic control or sliding mode control

- Digital versus analogue

- 2 control loops (analogue control + digital supervisor)

- Full digital low-losses controller demonstrated (limitations in transient performances)

- Systematic stability of closed-loop DC/DC quite complex (sample data modeling)

- **CAE** quite complex

# Wrap-up

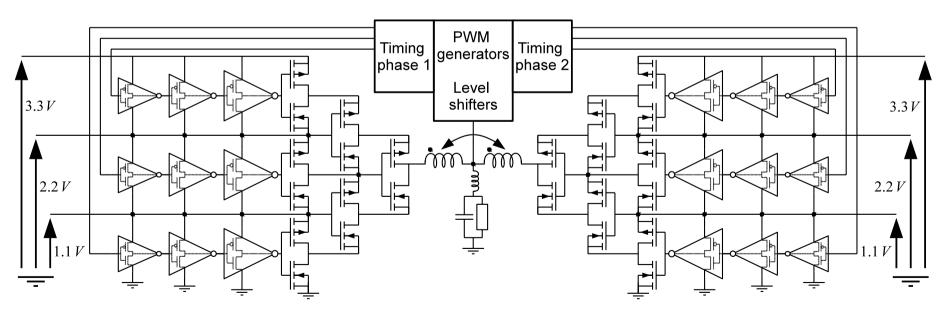

#### +100MHz switching frequency → phase coupling

RDS<sub>ON</sub>

Standard cell

2-phases

**Coupled 2-phases**

3-levels

#### ♦ Efficiency flatness → phase shedding

#### Air inductors versus magnetic devices:

- Cost, complexity

- EMI is an issue

- Coupling of inductors → magnetic material

#### Separate issues, separate technologies

- Interposer of passive devices

- Enable trench capacitors

### **♦ Motivations for PowerSWIPE HF DC/DC**

#### PowerSWIPE consortium

**BOSCH**

Tyndall National Institute, University College Cork

> IPDiA, Caen

Ampère Laboratory – University of Lyon, INSA Lyon, Lyon

Centro de Electrónica Industrial – Universidad Politécnica de Madrid Robert Bosch GmbH

> Infineon Technologies AG

Infineon Technologies Austria Villach AG

**Tyndall**

CETURM Centro de Electronica Industrial

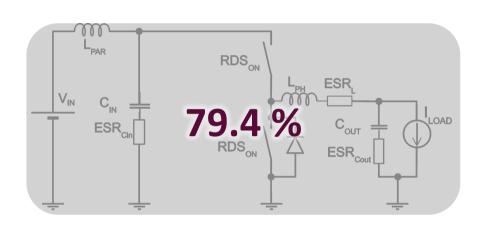

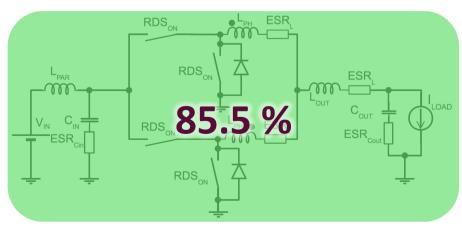

#### **Schematic**

Kursun, V., Narendra, S. G., De, V. K., & Friedman, E. G. (2005). Cascode monolithic DC-DC converter for reliable operation at high input voltages. Analog Integrated Circuits and Signal Processing, 42(3), 231-238 → evaluation by simulation

Peng et al., 2013, A 100 MHz two-phase four-segment DC-DC converter with light load efficiency enhancement in 0.18 μm CMOS. IEEE Trans. Circ. & Syst. I, 60(8):2213–2224.

- 40nm bulk CMOS

- **♦ Interposer by IPDIA and Tyndall**

- **♦ Hard switching then Hysteretic control**

See details on design on poster #9 by Florian Neveu

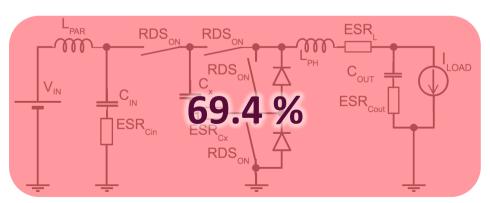

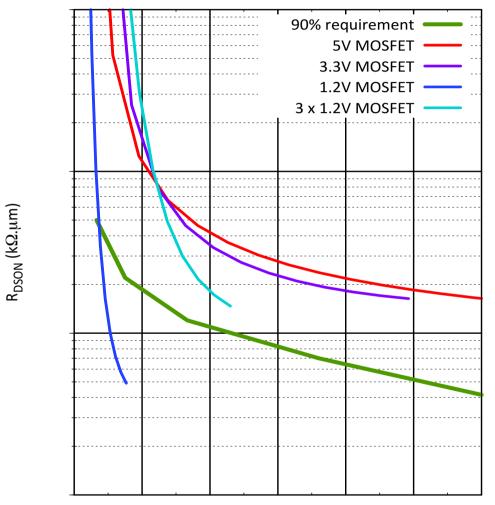

# Motivation for low-voltage MOSFET

Standard DC/DC step-down

- Analytical model of losses

- **Low-voltage MOSFET**

- Digital MOSFET could be considered

- Similar conclusions in any thin technology

Gate charge (fC.μm<sup>-1</sup>)

400 350

300

250

200150100

50

Current (mA)

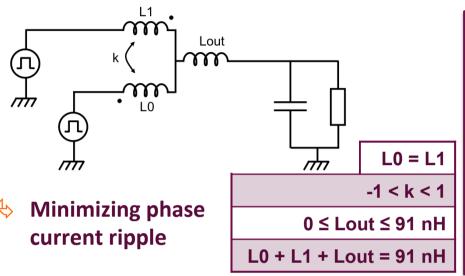

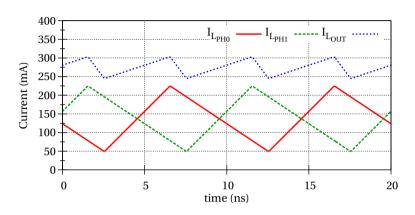

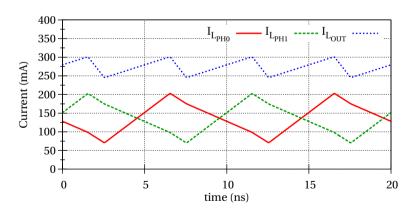

# Local optimization of coupled inductors

20

**#2 : Lout = 0 nH,** L0 = L1 = 45.5 nH, k = 0.4 **Ripple:** Phases: 151 mA, Output: 102 mA

10

time (ns)

**#1:** k = 0, L0 = L1 = 45.5 nH, Lout = 0 nH **Ripple:** Phases: 172 mA, Output: 56 mA

**#3:** L0 = L1 = 35 nH, Lout = 21 nH, k = 1 **Ripple:** Phases: 123 mA, Output: 55 mA

15

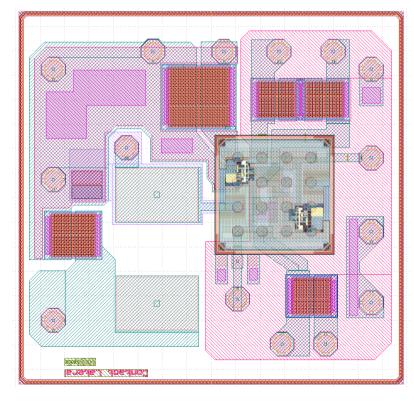

# **Primary PLS results**

# Perspectives

- Waiting for silicon delivery

- Multi-chip test board

- **Verification of limits of robustness**

- Multi-phase design

- **Optimized IC layout**

- **Optimized interposer layout**